1. Penahan Transistor

Pada gambar di atas , setiap kolektor menggerakkan basis yang berseberangan melalui sebuah resistor 100 K ohm. Pada rangkaian seperti ini, satu diantara transistor-transistor itu mengalami kejenuhan (saturasi) dan yang lain dalam keadaan terpancung (cutoff).

Misal transistor kanan yang jenuh, maka tegangan kolektornya akan mendekati 0V. Yang berarti tidak ada masukan penggerak bagi transistor sebelah kiri. Akibatnya transistor tersebut terpancung dan tegangan kolektornya mendekati +5V. nilai tegangan ini menghasilkan arus basis yang cukup besar pada basis transistor sebelah kanan untuk mempertahankan keadaan jenuhnya. Jadi, seluruh rangkaian ditahan (latched) pada keadaan dengan transistor sebelah kiri terpancung dan transistor sebelah kanan dalan keadaan jenuh. Titik Q bertegangan kurang lebih 0V dalam keadaan ini.

Uraian serupa berlaku jika transistor sebelah kiri yang jenuh, dan transistor sebelah kanan dalam keadaan terpancung. Gambar disamping menjelaskan keadaan tersebut. Dalam kasus ini, tegangan titik Q mendekati 5V.

Keluaran Q dapat merupakan keadaan rendah atau tinggi, yang berarti biner 0 atau 1. Keadaan tertahaan yang ditunjukkan oleh gambar diatas berarti rangkaian sedang menyimpan biner 0 sebab Q=0.

Di pihak lain, bila rangkaian tertahan sebagaimana ditunjukkan oleh gambar di samping, maka ini berarti rangkaian sedang menyimpan biner 1, sebab Q=1.

2. Penahan NOR

Gambar a di samping menunjukkan bagaimana cara menyusun sebuah rangkaian penahan dengan menggunakan gerbang NOR. Gambar b adalah ekivalen De Morgan dari rangkaian tersebut.

Sebagaimana disajikan oleh tabel di atas, R dan S yang rendah akan memberikan keadaan tak aktif : rangkaian tetap menyimpan atau mengingat keadaan semula. Masukan R yang rendah dan S yang tinggi memberikan keadaan set, sementara R yang tinggi dan S yang rendah mengungkapkan keadaan reset. Akhirnya, R dan S yang tinggi menimbulkan keadaan pacu. Karena itu kita harus menghindari keadaan masukan R=1 dan S=1 dalam menggunakan penahan NOR.

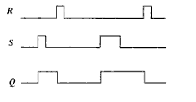

Diagram diatas merupakan diagram pewwaktuan yang memberi gambaran bagaimana sinyal-sinyal masukan berinteraksi untuk menghasilkan sinyal keluaran. terlihat bahwa keluaran Q menjadi tinggi ketika S berubah menjadi tinggi. ketika S kembali menjadi rendah, Q tetap bertahan dalam keadaan tinggi. Selanjutnya Q akan kembali menjadi rendah saat Rmenjadi tinggidan keadaan ini tetap bertahan sesudah R kembali menjadi rendah.

3. Panahan NAND

Flip-flop RS juga dapat disusun denganmenggunakan gerbang NAND seperti yang ditampilkan pada gambar a diatas, dan gambar b di sampingnya merupakan rangkaian ekivalen De Morgannya.

Untuk kedua rangkaian ini, bila R rendah dan S tinggi, Q akan di set menjadi tinggi dan sebaliknya, bila R tinggi dan S rendah, Q akan di redet menjadi rendah.

Karena sifat inversi gerbang NAND, keadaan pacuan dan keadaan tak aktif terjadi pada masukan yang terbalik. dengan kata lain, R=1 dan S=1 menjadi keadaan tak tak aktif, sementara R=0 dan S=0 menjadi keadaan pacuan.

Dengan ini, jika kita menggunakan gerbang NAND maka keadaan masukan yang harus dihindari adalah masukan yang sama-sama rendah pada waktu bersamaan.

Diagram pengaturan waktu dari penahan NAND dilukiskan seperti pada gambar diatas. Dalam keadaan normal R dan S harus tinggi untuk menghindari keadaan pacu. Selama beroperasi hanya satu diantara masukan yang diperbolehkan menjadi rendah. sebagaimana terlihat, keluaran Q menjadi tinggi ketika R menjadi rendah dan Q kembali pada keadaan rendah pada saat S menjadi rendah.

Flip-Flop D

Oleh karena flip-flop RS mudah terkena keadaan pacu, perlu dilakukan modifikasi desainnya untuk menghilangkan kemungkinan terjadinya keadaan tersebut. Hasilnya adalah flip-flop jenis baru yang dikenal sebagai penahan D.

1. Jenis tanpa Pendetak

Dengan menggunakan sebuah pembalik, bit data D memberikan masukan S kepada gerbang NAND dan komplemen D menggerakkan masukan R. Dengan ini penahan akan di set jika jika D tinggi dan di reset jika D rendah. Operasi ini di rangkum pada tabel di bawah.

Yang penting disini adalah bahwa di tabel kebenaran ini tidak terdapat keadaan pacu. Inverter akan selalu menjamin bahwa masukan S dan R berada dalam kemungkinan yang berlawanan. Sehingga tidak mungkin terjadi keadaan pacu.

Penahan D seperti ini tidak menggunakan sinyal pendetak. rangkaian akan di set atau di reset pada saat D menjadi tinggi atau rendah. flip-flop jenis ini hampir tidak pernah dipakai.

2. Jenis dengan Sinyal Pendetak

Gambar di atas menunjukkan rangkaian penahan D yang diatur oleh tingkat logika dari sinyal detak. CLK yang rendah akan membuat gerbang masukan tak aktif dan mencegah perubahan keadaan pada penahan. Dengan kata lain, pada waktu CLK rendah, penahan berada pada keadaan tak aktif dan rangkaian dikatakan sedang menyimpan atau mengingat. dipihak lain, bila CLK tinggi, masukan D mengendalikan keluaran. Dalam keadaan ini penahan akan di set oleh D yang tinggi dan di reset oleh D yang rendah.

Tabel dibawah merangkumkan hasil-hasil operasi tersebut.

Tanda X menyatakan keadaan yang tak perduli; boleh mewakili 0 atau 1. Selama CLK berada dalam keadaan rendah, keluaran tidak mengalami perubahan, lepas dari keadaan masukan D.akan tetapi jika CLK tinggi, keadaan keluaran sama dengan masukannya :Q=D.

Diagram pewaktuan yang menggambarkan proses ini disajikan oleh gambar dibawah ini.

Jika sinyal detak rendah, rangkaian ditahan pada keadaan semula dan keluaran Q tidak dapat diubah. Namun selama sinyal pendetak berada pada tingkat logika tinggi, keluaran Q sama dengan D; bila D tinggi, Q menjadi tinggi; dan bila D rendah, Q menjadi rendah. Dalam keadaan ini penahan bersifat tembus cahaya atau transparent. artinya keluaran mengikuti nilai masukan D sewaktu sinyal detak dalam keadaan tinggi.

Register Geser (rangkaian D flip-flop)

Gambar di atas menunjukkan sebuah register geser yang tersusun dari empat buah flip-flop D. Data input (D in) merupakan masukan dari flip-flop paling kanan. Q pada FF0 mengumpani FF1; Q pada FF1 memberikan masukan untuk FF2; dan seterusnya. Jadi pada saat tibanya tepi positif dari sinyal pewaktu yang berikutnya, bit-bit yang tersimpan berpindah satu posisi ke kiri.

Sebagai contoh, kita ikuti apa yang terjadi jika D in = 1 dan Q=0000

Semua masukan data sama dengan 0 kecuali masukan di bagian paling kanan Ketika tepi positif dari sinyal pewaktu yang pertama masuk, FF0 aktif menyimpan D in dan kata yang tersimpan menjadi :Q=0001

Munculnya kata yang baru ini berarti D pada FF1 sekarang samadengan 1, sebagaimana keadaan D pada FF0. Pada teepi positif berikutnya, FF1 melaksanakan fungsinya dan isi register menjadi Q=0011

Pada tepi positif ketiga, isi register menjadi Q=0111

dan tepi naik ke empat dari sinyal pewaktu memberikan Q=1111

Setelah itu kata yang tersimpan tidak akan berubah selama D in =1

Andaikan seekarang D in di ubah menjadi 0. Pulsa lonceng yang berturut-turut akan menghasilkan isi-isi register sebagai berikut; Q=1110; Q=1100; Q=1000; Q=0000. Jadi selama D in =0 pulsa-pulsa lonceng berikutnya tidak berpengaruh lebih lanjut.

Flip-flop JK

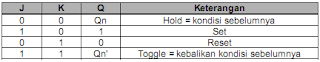

|

| Rangkaian Dasar JKFF |

|

| Tabel Kebenaran JKFF |

|

| Diagram Waktu JKFF |

FF-JK dibangun dari 2 buah FF-SR yang dihubungkan menjadi satu, yaitu keluaran FF-SR pertama menjadi masukan FF-SR kedua dan keluaran FF-SR kedua menjadi masukan FF-SR pertama. FF-SR pertama disebut "master", FF-SR kedua disebut "slave". Hubungan kedua FF-SR tersebut ditunjukkan dalam Gambar diatas.

Hold : bila J dan K rendah, maka Q dalam kondisi NC(not change) tetap mempertahankan kondisi sebelumnya.

Reset : bila J rendah dan K tinggi, gerbang bagian atas tak berfungsi sehingga flip-flop tidak dapat diset. Satu-satunya langkah yang mungkin diambil adalah melakukan reset. Bila Q tinggi, gerbang bagian bawah akan melewatkan sebuah sinyal pemucu reset segera setibanya tepi positif dari sinyal detak. Ini akan menyebabkan Q menjadi rendah. Berarti flip-flop direset oleh tepi naik dari sinyal detak.

Set : bila J tinggi dan K rendah, gerbang bagian bawah tidak berfungsi dan tidak mungkin melakukan reset terhadap flip-flop, akan tetapi flip-flop dapat di set sebagai berikut. Ketika Q rendah, Q' menjadi tinggi. Karena itu gerbang bagian atas akan melewatkan sebuah sinyal pemicu set pada tepi positif dari sinyal detak. keadaan ini akan menghasilkan keluaran Q yang tinggi. Ini berarti flip-flop diset oleh tepi positif dari sinyal detak berikutnya.

Toggle : bila J dan K tinggi, flip-flop dapat diset atau direset. Bergantung pada keadaan arus dari keluaran. Jadi J=1 dan K=1 berarti bahwa flip-flop akan togel pada tepi positif dari sinyal detak berikutnya.(Toggle berarti beralih kepada keadaan yang berlawanan).

Pencacah Naik

Pencacah naik merupakan suatu pencacah menghitung ”naik” dari bilangan yang kecil ke bilangan yang lebih besar.yaitu dari 0000 sampai 1111.

Berikut ini adalah gambar dari Pencacah naik :PENJELASANNYA: Pencacah naik merupakan suatu counter menghitung bilangan biner dari 0000 ke 1111. Jadi setiap FLIP-FLOP outputnya berada di Q kemudian masuk ke FLIP-FLOP berikutnya sebagai sebuah CLOCK. Supaya Pencacah naik ini bisa diset frekuensi yang diinginkan maka ada CLEAR(CLR)untuk mengembalikan OUTPUT yang tadinya tinggi menjadi rendah lagi. Dengan bantuan NAND dan AND.

Pencacah Putar

Adalah suatu pencacah yang menghasilkan kata dengan 1-bit tinggi, yang digeser satu posisi pada setiap pulsa detak. Jadi sebuah pencacah putar tidak mencacah dengan bilangan biner tetapi bekerja dengan kata-kata yang hanya memiliki satu bit tinggi.

anandaekasetiawan.comoj.com/web_documents/p4-flip-flop.pdf

Malvino,A.P.,1983.Elektronika Komputer Digital.Jakarta:Erlangga

0 komentar:

Posting Komentar

silahkan dikomen....